# Simulink<sup>®</sup> PLC Coder™ User's Guide

# MATLAB&SIMULINK®

**R**2017a

#### How to Contact MathWorks

| Latest news:        | www.mathworks.com                    |

|---------------------|--------------------------------------|

| Sales and services: | www.mathworks.com/sales_and_services |

| User community:     | www.mathworks.com/matlabcentral      |

| Technical support:  | www.mathworks.com/support/contact_us |

| Phone:              | 508-647-7000                         |

The MathWorks, Inc. 3 Apple Hill Drive Natick, MA 01760-2098

#### $Simulink^{\mathbb{R}}$ PLC Coder<sup>TM</sup> User's Guide

#### © COPYRIGHT 2010–2017 by The MathWorks, Inc.

The software described in this document is furnished under a license agreement. The software may be used or copied only under the terms of the license agreement. No part of this manual may be photocopied or reproduced in any form without prior written consent from The MathWorks, Inc.

FEDERAL ACQUISITION: This provision applies to all acquisitions of the Program and Documentation by, for, or through the federal government of the United States. By accepting delivery of the Program or Documentation, the government hereby agrees that this software or documentation qualifies as commercial computer software or commercial computer software documentation as such terms are used or defined in FAR 12.212, DFARS Part 227.72, and DFARS 252.227-7014. Accordingly, the terms and conditions of this Agreement and only those rights specified in this Agreement, shall pertain to and govern the use, modification, reproduction, release, performance, display, and disclosure of the Program and Documentation by the federal government (or other entity acquiring for or through the federal government) and shall supersede any conflicting contractual terms or conditions. If this License fails to meet the government's needs or is inconsistent in any respect with federal procurement law, the government agrees to return the Program and Documentation, unused, to The MathWorks, Inc.

#### Trademarks

MATLAB and Simulink are registered trademarks of The MathWorks, Inc. See www.mathworks.com/trademarks for a list of additional trademarks. Other product or brand names may be trademarks or registered trademarks of their respective holders.

#### Patents

MathWorks products are protected by one or more U.S. patents. Please see www.mathworks.com/patents for more information.

T

#### **Revision History**

| 1. 1. 0.01.0   | o 11 - 1    |

|----------------|-------------|

| March 2010     | Online only |

| September 2010 | Online only |

| April 2011     | Online only |

| September 2011 | Online only |

| March 2012     | Online only |

| September 2012 | Online only |

| March 2013     | Online only |

| September 2013 | Online only |

| March 2014     | Online only |

| October 2014   | Online only |

| March 2015     | Online only |

| September 2015 | Online only |

| March 2016     | Online only |

| September 2016 | Online only |

| March 2017     | Online only |

|                |             |

New for Version 1.0 (Release 2010a) Revised for Version 1.1 (Release 2010b) Revised for Version 1.2 (Release 2011a) Revised for Version 1.2.1 (Release 2011b) Revised for Version 1.3 (Release 2012a) Revised for Version 1.4 (Release 2012b) Revised for Version 1.5 (Release 2013a) Revised for Version 1.6 (Release 2013b) Revised for Version 1.6 (Release 2013b) Revised for Version 1.7 (Release 2014a) Revised for Version 1.8 (Release 2014b) Revised for Version 1.9 (Release 2015b) Revised for Version 2.0 (Release 2015b) Revised for Version 2.1 (Release 2016a) Revised for Version 2.2 (Release 2016b) Revised for Version 2.3 (Release 2017a)

# Contents

#### **Getting Started**

| Simulink PLC Coder Product Description                             | 1-2<br>1-2 |

|--------------------------------------------------------------------|------------|

| PLC Code Generation in the Development Process                     | 1-3        |

| Expected Users                                                     | 1-4        |

| Glossary                                                           | 1-4        |

| System Requirements                                                | 1-5        |

| Supported IDE Platforms                                            | 1-6        |

| IDEs Supported for Structured Text Generation                      | 1-6        |

| IDEs Supported for Ladder Diagram Code Generation                  | 1-7        |

| PLC Code Generation Workflow                                       | 1-8        |

| Prepare Model for Structured Text Generation                       | 1-9        |

| Tasking Mode                                                       | 1-9        |

| Solvers                                                            | 1-9        |

| Configuring Simulink Models for Structured Text Code<br>Generation | 1-9        |

| Checking System Compatibility for Structured Text Code             |            |

| Generation                                                         | 1-14       |

| Generate and Examine Structured Text Code                          | 1-17       |

| Generate Structured Text from the Model Window                     | 1-17       |

| Generate Structured Text with the MATLAB Interface                 | 1-19       |

| View Generated Code                                                | 1-20       |

| Propagate Block Descriptions to Code Comments                      | 1-22       |

| Files Generated with Simulink PLC Coder                            | 1-23       |

| Specify Custom Names for Generated Files                           | 1-26       |

| Import Structured Text Code Automatically                | 1-27 |

|----------------------------------------------------------|------|

| PLC IDEs That Qualify for Importing Code Automatically . | 1-27 |

| Generate and Automatically Import Structured Text Code . | 1-27 |

| Troubleshoot Automatic Import Issues                     | 1-28 |

| Simulation and Code Generation of Motion Instructions    | 1-31 |

| Workflow for Using Motion Instructions in Model          | 1-31 |

| Library of Motion Instructions                           | 1-34 |

| Data Types for Motion Instructions                       | 1-34 |

|                                                          |      |

#### Mapping Simulink Semantics to Structured Text

| Generated Code Structure for Simple Simulink<br>Subsystems                                                                                         | 2-2                |

|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| Generated Code Structure for Reusable Subsystems                                                                                                   | 2-4                |

| Generated Code Structure for Triggered Subsystems                                                                                                  | 2-7                |

| Generated Code Structure for Stateflow Charts<br>Stateflow Chart with Event Based Transitions<br>Stateflow Chart with Absolute Time Temporal Logic | 2-9<br>2-9<br>2-11 |

| Generated Code Structure for MATLAB Function Block                                                                                                 | 2-14               |

| Generated Code Structure for Multirate Models                                                                                                      | 2-16               |

| Generated Code Structure for Subsystem Mask<br>Parameters                                                                                          | 2-18               |

| Global Tunable Parameter Initialization for PC WORX                                                                                                | 2-23               |

| Ladder Diagram Generation for PLC Controllers      | 3-2  |

|----------------------------------------------------|------|

| Ladder Diagram Generation Workflow                 | 3-4  |

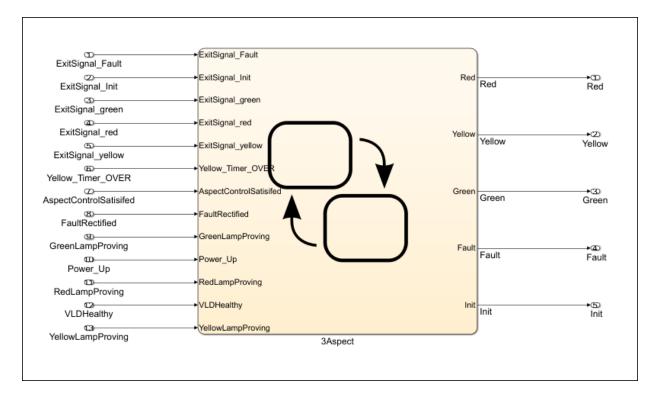

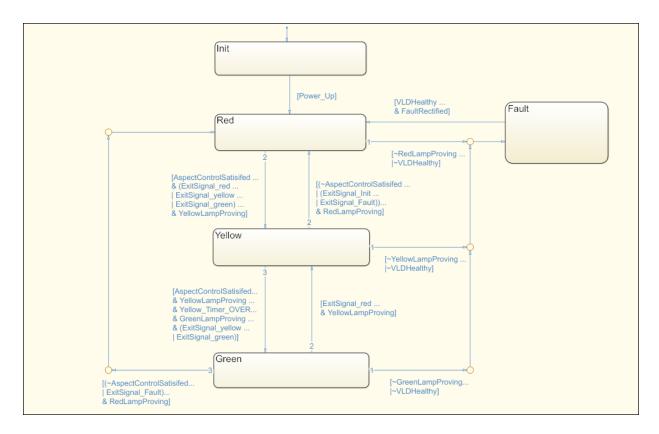

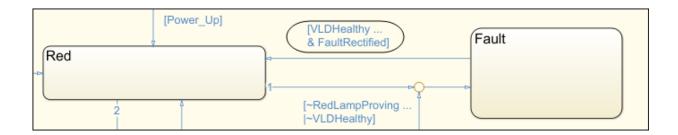

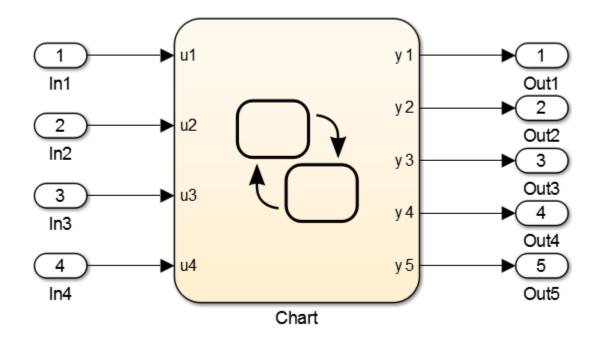

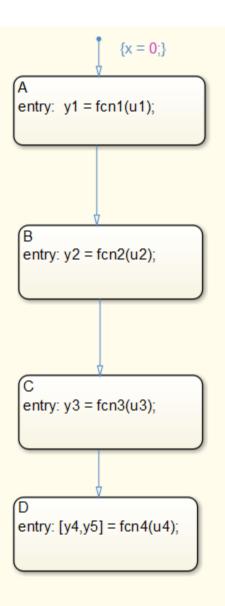

| Prepare Chart for Ladder Diagram Generation        | 3-6  |

| Design PLC Application with Stateflow              | 3-6  |

| Create Test Harness for Chart                      | 3-7  |

| Generate Ladder Diagram Code from Stateflow Chart  | 3-10 |

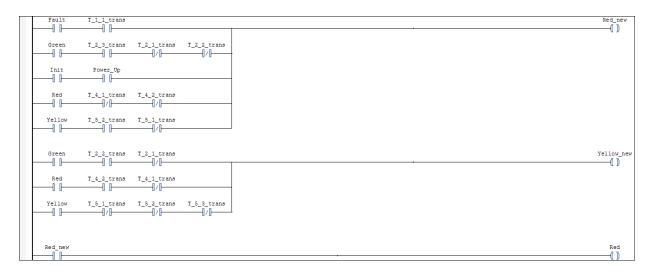

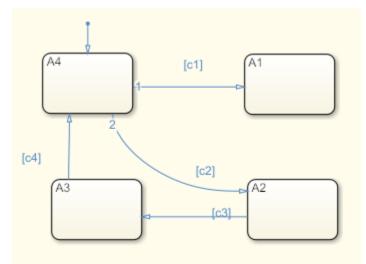

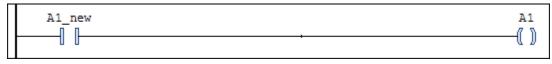

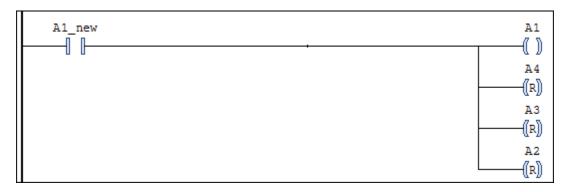

| Stateflow Chart and Ladder Logic Diagram           | 3-10 |

| Generate Ladder Diagram from Chart                 | 3-13 |

| Generate Ladder Diagram Along with Test Bench      | 3-13 |

| Import Ladder Diagram Code to CODESYS 3.5 IDE and  |      |

| Validate Diagram                                   | 3-15 |

| Import Ladder Diagram XML                          | 3-15 |

| Verify Ladder Diagram with Test Bench              | 3-18 |

| Restrictions on Stateflow Chart for Ladder Diagram |      |

| Generation                                         | 3-19 |

#### Generating Test Bench Code

## 4

| How Test Bench Verification Works                     | 4-2 |

|-------------------------------------------------------|-----|

| Integrate Generated Code with Custom Code             | 4-3 |

| Import and Verify Structured Text Code                | 4-4 |

| Generate, Import, and Verify Structured Text          | 4-4 |

| Import and Verify Structured Text to KW-Software      |     |

| MULTIPROG 5.0 and Phoenix Contact PC WORX 6.0         |     |

| IDEs                                                  | 4-5 |

| Troubleshooting: Long Test Bench Code Generation Time | 4-6 |

| Verify Generated Code with Multiple Test Benches      | 4-7 |

| Troubleshooting: Test Data Exceeds Target Data Size   | 4-9 |

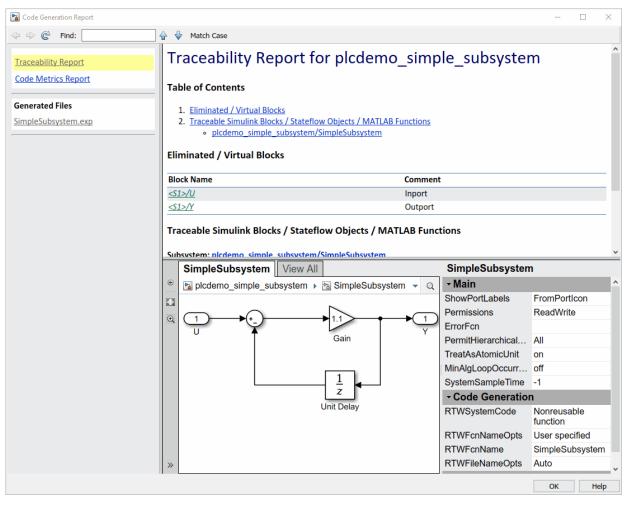

| Information in Code Generation Reports               | 5-2  |

|------------------------------------------------------|------|

| Create and Use Code Generation Reports               | 5-4  |

| Generate a Traceability Report from Configuration    |      |

| Parameters                                           | 5-4  |

| Keep the Report Current                              | 5-6  |

| Trace from Code to Model                             | 5-7  |

| Trace from Model to Code                             | 5-8  |

| Model Web View in Code Generation Report             | 5-9  |

| Generate a Static Code Metrics Report                | 5-13 |

| Generate a Traceability Report from the Command Line | 5-14 |

| View Requirements Links from Generated Code          | 5-16 |

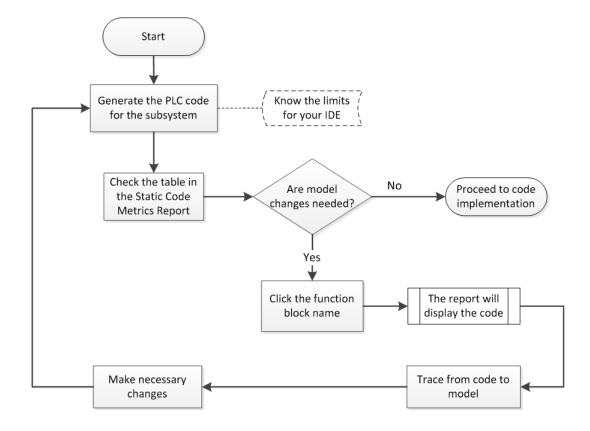

| Working with the Static Code Metrics Report          | 5-17 |

| Workflow for Static Code Metrics Report              | 5-17 |

| Report Contents                                      | 5-18 |

| Function Block Information                           | 5-19 |

#### Working with Tunable Parameters in the Simulink PLC Coder Environment

### 6

| Block Parameters in Generated Code                     |     |

|--------------------------------------------------------|-----|

| Control Appearance of Block Parameters in Generated    |     |

| Code                                                   | 6-5 |

| Configure Tunable Parameters with Simulink.Parameter   |     |

| Objects                                                | 6-5 |

| Make Parameters Tunable Using Configuration Parameters |     |

| Dialog Box                                             | 6-8 |

| Control Code Partitions for Subsystem Block              | . 7-3 |

|----------------------------------------------------------|-------|

| Control Code Partitions Using Subsystem Block Parameters | . 7-3 |

| One Function Block for Atomic Subsystems                 | 7-6   |

| One Function Block for Virtual Subsystems                | . 7-7 |

| Multiple Function Blocks for Nonvirtual Subsystems       | 7-8   |

7

8

9

#### **Integrating Externally Defined Symbols**

| Integrate Externally Defined Symbols              | 8-2 |

|---------------------------------------------------|-----|

| Integrate Custom Function Block in Generated Code | 8-3 |

#### **IDE-Specific Considerations**

| Integrate Generated Code with Siemens IDE Project<br>Integrate Generated Code with Siemens SIMATIC STEP 7 | 9-2<br>9-2 |

|-----------------------------------------------------------------------------------------------------------|------------|

| Projects                                                                                                  | 9-2<br>9-2 |

|                                                                                                           |            |

| Use Internal Signals for Debugging in RSLogix 5000 IDE                                                    | 9-4        |

| Rockwell Automation RSLogix Considerations                                                                | 9-6        |

| Add-On Instruction and Function Blocks                                                                    | 9-6        |

| Double-Precision Data Types                                                                               | 9-6        |

| Unsigned Integer Data Types                                                                               | 9-6        |

| Unsigned Fixed-Point Data Types                                                                           | 9-6        |

| Enumerated Data Types                      | 9-7 |

|--------------------------------------------|-----|

| Considerations for Siemens IDEs            | 9-8 |

| Double-Precision Floating-Point Data Types | 9-8 |

| int8 and Unsigned Integer Types            | 9-8 |

| Unsigned Fixed-Point Data Types            | 9-8 |

| Enumerated Data Types                      | 9-9 |

| INOUT Variables                            | 9-9 |

#### Supported Simulink and Stateflow Blocks

# 10

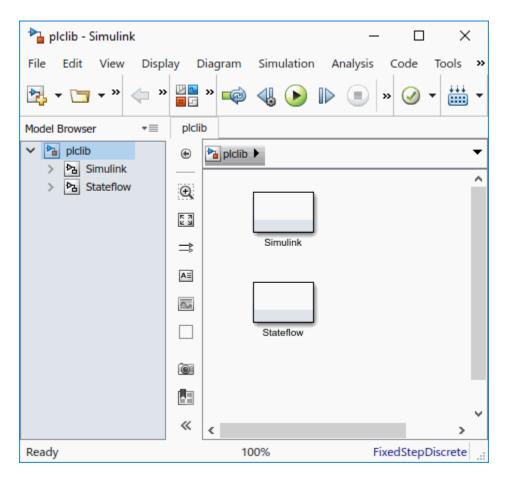

| Supported Blocks               | 10-2    |

|--------------------------------|---------|

| View Supported Blocks Library  | 10-2    |

| Supported Simulink Blocks      | 10-3    |

| Supported Stateflow Blocks     | 10 - 12 |

| Blocks With Restricted Support | 10 - 12 |

#### Limitations

| Coder Limitations                         | 11- |

|-------------------------------------------|-----|

| Current Limitations                       | 11- |

| rand Function Support Limitations         | 11- |

| Workspace Parameter Data Type Limitations | 11- |

| Traceability Report Limitations           | 11- |

| Fixed-Point Data Type Limitations         | 11- |

| Multirate Model Limitations               | 11- |

| Permanent Limitations                     | 11- |

#### Configuration Parameters for Simulink PLC Coder Models

| PLC Coder: General                                          | 13-2    |

|-------------------------------------------------------------|---------|

| PLC Coder: General Tab Overview                             | 13-4    |

| Target IDE                                                  | 13-5    |

| Show Full Target List                                       | 13-8    |

| Target IDE Path                                             | 13-10   |

| Code Output Directory                                       | 13-12   |

| Generate Testbench for Subsystem                            | 13-13   |

| PLC Coder: Comments                                         | 13-14   |

| Comments Overview                                           | 13 - 15 |

| Include Comments                                            | 13 - 15 |

| Include Block Description                                   | 13-16   |

| Simulink Block / Stateflow Object Comments                  | 13-17   |

| Show Eliminated Blocks                                      | 13-18   |

| PLC Coder: Optimization                                     | 13-19   |

| Optimization Overview                                       | 13-20   |

| Signal Storage Reuse                                        | 13 - 21 |

| Remove Code from Floating-point to Integer Conversions That |         |

| Wraps Out-Of-Range Values                                   | 13-23   |

| Generate Reusable Code                                      | 13-24   |

| Loop Unrolling Threshold                                    | 13-26   |

| PLC Coder: Symbols                                          | 13-27   |

| Symbols Overview                                            | 13-29   |

| Maximum Identifier Length                                   | 13-30   |

| Use the Same Reserved Names as Simulation Target            | 13-31   |

| Reserved Names                                              | 13-32   |

| Externally Defined Symbols                                  | 13-33   |

| Preserve Alias Type Names for Data Types                    | 13 - 33 |

| PLC Coder: Report            | 13-36   |

|------------------------------|---------|

| Report Overview              | 13 - 37 |

| Generate Traceability Report | 13 - 37 |

| Generate Model Web View      | 13 - 38 |

# **Getting Started**

- "Simulink PLC Coder Product Description" on page 1-2

- "PLC Code Generation in the Development Process" on page 1-3

- "Supported IDE Platforms" on page 1-6

- "PLC Code Generation Workflow" on page 1-8

- "Prepare Model for Structured Text Generation" on page 1-9

- "Generate and Examine Structured Text Code" on page 1-17

- "Propagate Block Descriptions to Code Comments" on page 1-22

- "Files Generated with Simulink PLC Coder" on page 1-23

- "Specify Custom Names for Generated Files" on page 1-26

- "Import Structured Text Code Automatically" on page 1-27

- "Simulation and Code Generation of Motion Instructions" on page 1-31

#### Simulink PLC Coder Product Description Generate IEC 61131-3 Structured Text and ladder diagrams for PLCs and PACs

Simulink<sup>®</sup> PLC Coder<sup>™</sup> generates hardware-independent IEC 61131-3 Structured Text and ladder diagrams from Simulink models, Stateflow<sup>®</sup> charts, and MATLAB<sup>®</sup> functions. The Structured Text and ladder diagrams are generated in PLCopen XML and other file formats supported by widely used integrated development environments (IDEs) including 3S-Smart Software Solutions CODESYS, Rockwell Automation<sup>®</sup> Studio 5000, Siemens<sup>®</sup> TIA Portal, and OMRON<sup>®</sup> Sysmac<sup>®</sup> Studio. As a result, you can compile and deploy your application to numerous programmable logic controller (PLC) and programmable automation controller (PAC) devices.

Simulink PLC Coder generates test benches that help you verify the Structured Text and ladder diagrams using PLC and PAC IDEs and simulation tools. It also provides code generation reports with static code metrics and bidirectional traceability between model and code. Support for industry standards is available through IEC Certification Kit (for IEC 61508 and IEC 61511).

#### **Key Features**

- · Automatic generation of IEC 61131-3 Structured Text and ladder diagrams

- IDE support, including 3S-Smart Software Solutions CODESYS, Rockwell Automation Studio 5000, Siemens TIA Portal, OMRON Sysmac Studio, and PLCopen XML

- Simulink support, including reusable subsystems, PID controller blocks, and lookup tables

- · Stateflow support, including state machines, graphical functions, and truth tables

- MATLAB support, including if-else statements, loop constructs, and math operations

- Support for multiple data types, including Boolean, integer, enumerated, and floatingpoint, as well as vectors, matrices, buses, and tunable parameters

- Test bench creation

#### PLC Code Generation in the Development Process

Simulink PLC Coder software lets you generate IEC 61131-3 compliant Structured Text code from Simulink models. This software brings the Model-Based Design approach into the domain of PLC and PAC development. Using the coder, system architects and designers can spend more time fine-tuning algorithms and models through rapid prototyping and experimentation, and less time on coding PLCs.

Typically, you use a Simulink model to simulate a design for realization in a PLC. Once satisfied that the model meets design requirements, run the Simulink PLC Coder compatibility checker utility. This utility verifies compliance of model semantics and blocks for PLC target IDE code generation compatibility. Next, invoke the Simulink PLC Coder tool, using either the command line or the graphical user interface. The coder generates Structured Text code that implements the design embodied in the model.

Usually, you also generate a corresponding test bench. You can use the test bench with PLC emulator tools to drive the generated Structured Text code and evaluate its behavior.

The test bench feature increases confidence in the generated code and saves time spent on test bench implementation. The design and test process are fully iterative. At any point, you can return to the original model, modify it, and regenerate code.

At completion of the design and test phase of the project, you can easily export the generated Structure Text code to your PLC development environment. You can then deploy the code.

Using Simulink PLC Coder, you can also generate Ladder Diagram code for your applications from a Stateflow chart. The benefits are:

- You can design your application by using states and transitions in a Stateflow chart. Once you complete the design, you can generate Ladder Diagram code in XML or another format. You then import the generated code to an IDE such as CODESYS 3.5 or RSLogix<sup>™</sup> AOI 5000 and view the ladder diagram.

- When you test your Stateflow chart by using a set of inputs, you can reuse these inputs to create a test bench for the Ladder Diagram code. You import the test bench to your PLC IDE and compare the results of simulation with the results of running the ladder diagram. If the results match, the original Stateflow chart is equivalent to the generated Ladder Diagram code.

#### **Expected Users**

The Simulink PLC Coder product is a tool for control and algorithm design and test engineers in the following applications:

- PLC manufacturing

- Machine manufacturing

- Systems integration

You should be familiar with:

- MATLAB and Simulink software and concepts

- PLCs

- Structured Text language

If you want to download generated code to a PLC IDE, you should also be familiar with your chosen PLC IDE platform. For a list of these platforms, see "Supported IDE Platforms" on page 1-6.

#### Glossary

| Term            | Definition                                                                                                                                                                                                                                                                    |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PAC             | Programmable automation controller.                                                                                                                                                                                                                                           |  |

| PLC             | Programmable logic controller.                                                                                                                                                                                                                                                |  |

| IEC 61131-3     | IEC standard that defines the Structured Text language for which the Simulink PLC Coder software generates code.                                                                                                                                                              |  |

| PLCopen         | Vendor- and product-independent organization that works with the<br>IEC 61131-3 standard. The Simulink PLC Coder product can generate<br>Structured Text using the PLCopen XML standard format. See http://<br>www.plcopen.org/pages/tc6_xml/xml_intro/index.htm for details. |  |

| Structured Text | High-level textual language defined by IEC 61131-3 standard for the programming of PLCs.                                                                                                                                                                                      |  |

| function block  | Structured Text language programming concept that allows the encapsulation and reuse of algorithmic functionality.                                                                                                                                                            |  |

### System Requirements

For a list of related products, see System Requirements at the MathWorks<sup>®</sup> website.

### **Supported IDE Platforms**

#### **IDEs Supported for Structured Text Generation**

The Simulink PLC Coder product is tested with the following IDE platforms:

- 3S-Smart Software Solutions CODESYS Version 2.3 or 3.3 or 3.5 (SP4 or later)

- B&R Automation Studio<sup>®</sup> 3.0 or 4.0

- Beckhoff<sup>®</sup> TwinCAT<sup>®</sup> 2.11 or 3

- KW-Software MULTIPROG® 5.0 or 5.5

The Simulink PLC Coder software supports only the English version of KW-Software MULTIPROG target IDE.

- OMRON Sysmac Studio Version 1.04, 1.05, 1.09 or 1.12

- Phoenix Contact<sup>®</sup> PC WORX<sup>™</sup> 6.0

The Simulink PLC Coder software supports only the English version of Phoenix Contact PC WORX target IDE.

- Rexroth IndraWorks version 13V12 IDE

- Rockwell Automation RSLogix 5000 Series Version 17, 18, 19 or 20 and Rockwell Studio 5000 Logix Designer Version 21 or 24

Simulink PLC Coder can generate code for Add-On instructions (AOIs) and routine code. The software supports automatic import and verification of generated code only for the RSLogix IDEs and not the Studio 5000 IDE.

• Siemens SIMATIC<sup>®</sup> STEP<sup>®</sup> 7 Version 5.3, 5.4 or 5.5

The Simulink PLC Coder software assumes that English systems use English S7. It assumes that German systems use German S7.

- Siemens TIA Portal V13

- Generic

- PLCopen XML

For a list of supported IDEs and platforms, see Supported IDEs at the MathWorks website.

#### IDEs Supported for Ladder Diagram Code Generation

The Simulink PLC Coder product is tested with the following IDE platforms:

- 3S-Smart Software Solutions CODESYS Version 3.5 SP6

- Rockwell Automation RSLogix 5000 Series Version 20 and Rockwell Studio 5000 Logix Designer Version 24

- PLCopen XML

### PLC Code Generation Workflow

Your basic Simulink PLC Coder workflow is:

- 1 Define and design a Simulink model from which you want to generate code.

- **2** Identify the model components for which you want to generate code for importing to a PLC.

- **3** Place the components in a Subsystem block.

- **4** Identify your target PLC IDE.

- **5** Select a solver.

- **6** Configure the Subsystem block to be atomic.

- 7 Check that the model is compatible with the Simulink PLC Coder software.

- 8 Simulate your model.

- **9** Configure model parameters to generate code for your PLC IDE.

- **10** Examine the generated code.

- **11** Import code to your PLC IDE.

### Prepare Model for Structured Text Generation

#### In this section ...

"Tasking Mode" on page 1-9

"Solvers" on page 1-9

"Configuring Simulink Models for Structured Text Code Generation" on page 1-9

"Checking System Compatibility for Structured Text Code Generation" on page 1-14

#### **Tasking Mode**

This step is only required if your Simulink model contains multi-rate signals. If your Simulink model does not contain multi-rate signals, you may proceed to solver selection.

Simulink PLC Coder only generates code for single-tasking subsystems. For multirate subsystems, you must first explicitly set the tasking mode to single-tasking before selecting a solver. In the model configuration, on the Solver pane, clear the checkbox for **Treat each discrete rate as a separate task**.

#### **Solvers**

Choose a solver for your Simulink PLC Coder model.

| Model         | Solver Setting                                                                                        |

|---------------|-------------------------------------------------------------------------------------------------------|

| Variable-step | Use a continuous solver. Configure a fixed sample time for the subsystem for which you generate code. |

| Fixed-step    | Use a discrete fixed-step solver.                                                                     |

#### Configuring Simulink Models for Structured Text Code Generation

You must already have a model for which you want to generate and import code to a PLC IDE. Before you use this model, perform the following steps.

1 In the Command Window, open your model.

2 Configure the model to use the fixed-step discrete solver. Select Simulation > Model Configuration Parameters and in the Solver pane, set Type to Fixed-step and Solver to discrete (no continuous states).

If your model uses a continuous solver, has a subsystem, configure a fixed sample time for the subsystem for which you generate code.

- **3** Save this model as plcdemo\_simple\_subsystem1.

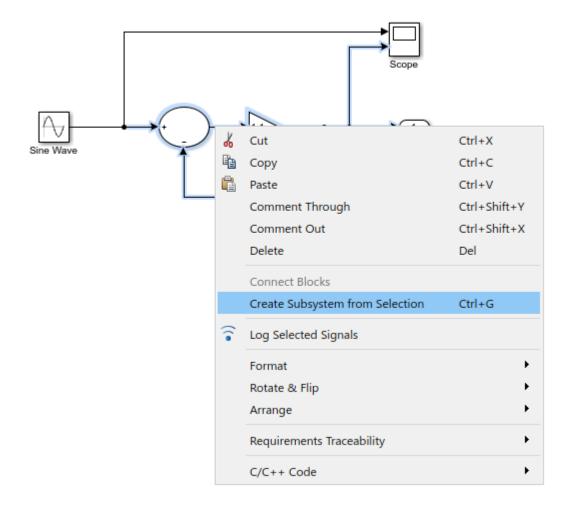

- **4** Create a subsystem containing the components for which you want to generate Structured Text code.

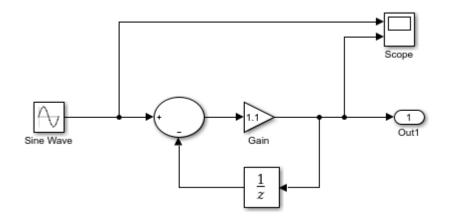

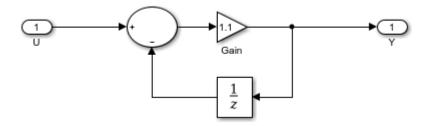

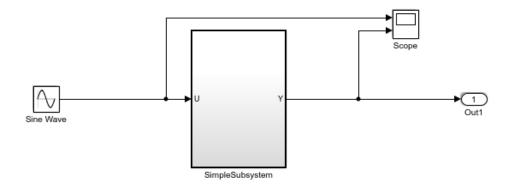

Optionally, rename In1 and Out1 to U and Y respectively. This operation results in a subsystem like the following figure:

- **5** Save the model with the new subsystem.

- **6** In the top-level model, right-click the Subsystem block and select **Block Parameters (Subsystem)**.

- 7 In the resulting block dialog box, select **Treat as atomic unit**.

| 🛅 Block Parameters: SimpleSubsystem 🛛 🗙                                                                               |

|-----------------------------------------------------------------------------------------------------------------------|

| Subsystem                                                                                                             |

| Select the settings for the subsystem block. To enable parameters for code generation, select 'Treat as atomic unit'. |

| Main Code Generation                                                                                                  |

| Show port labels FromPortIcon                                                                                         |

| Read/Write permissions: ReadWrite                                                                                     |

| Name of error callback function:                                                                                      |

| :                                                                                                                     |

| Permit hierarchical resolution: All                                                                                   |

| ☑ Treat as atomic unit                                                                                                |

| Minimize algebraic loop occurrences                                                                                   |

| Sample time (-1 for inherited):                                                                                       |

| -1 :                                                                                                                  |

| Treat as grouped when propagating variant conditions                                                                  |

|                                                                                                                       |

| OK Cancel Help Apply                                                                                                  |

- 8 Click OK.

- **9** Simulate your model.

- 10 Save your model. In later procedures, you can use either this model, or the plcdemo\_simple\_subsystem model that comes with your software.

You are now ready to:

- Set up your subsystem to generate Structured Text code. See "Checking System Compatibility for Structured Text Code Generation" on page 1-14.

- Generate Structured Text code for your IDE. See "Generate and Examine Structured Text Code" on page 1-17.

#### Checking System Compatibility for Structured Text Code Generation

You must already have a model that you have configured to work with the Simulink PLC Coder software.

- 1 In your model, navigate to the subsystem for which you want to generate code.

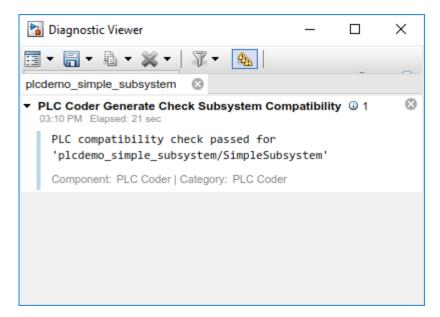

- 2 Right-click that Subsystem block and select PLC Code > Check Subsystem Compatibility.

The coder checks whether your model satisfies the Simulink PLC Coder criteria. When the checking is complete, a **View diagnostics** hyperlink appears at the bottom of the model window. Click this hyperlink to open the Diagnostic Viewer window.

|                                                | Signals or Ports             | · |                      |                            |

|------------------------------------------------|------------------------------|---|----------------------|----------------------------|

|                                                | Requirements Traceability    | + |                      |                            |

|                                                | Linear Analysis              | • |                      |                            |

|                                                | Design Verifier              | + |                      |                            |

|                                                | Coverage                     | + |                      |                            |

|                                                | Model Advisor                | ۲ |                      |                            |

|                                                | Fixed-Point Tool             |   |                      |                            |

| Simple:                                        | Model Transformer            | • |                      |                            |

| Simple                                         | C/C++ Code                   | • |                      |                            |

|                                                | HDL Code                     | • |                      |                            |

| is the code generated<br>To build the subsyste | PLC Code                     | • | Enable "Treat as ato | mic unit" to generate code |

| Code for Subsystem                             | Polyspace                    | • | Navigate to Code     |                            |

| ys hyperlinks to the g                         | Block Parameters (Subsystem) |   | erated files.        |                            |

| Convicts 2000                                  | Properties                   |   |                      |                            |

| Copyright 2009-:                               | Help                         |   |                      |                            |

|                                                |                              |   | -                    |                            |

|                                                |                              |   |                      |                            |

If the subsystem is not atomic, right-click the Subsystem block and select **PLC Code**, which prompts **Enable "Treat as atomic unit" to generate code**.

This command opens the block parameter dialog box. Select **Treat as atomic unit**.

| 🛅 Block Parameters: SimpleSubsystem 🛛 🕹                                                                               |

|-----------------------------------------------------------------------------------------------------------------------|

| Subsystem                                                                                                             |

| Select the settings for the subsystem block. To enable parameters for code generation, select 'Treat as atomic unit'. |

| Main Code Generation                                                                                                  |

| Show port labels FromPortIcon                                                                                         |

| Read/Write permissions: ReadWrite                                                                                     |

| Name of error callback function:                                                                                      |

|                                                                                                                       |

| Permit hierarchical resolution: All                                                                                   |

| Treat as atomic unit                                                                                                  |

| Minimize algebraic loop occurrences                                                                                   |

| Sample time (-1 for inherited):                                                                                       |

| -1                                                                                                                    |

| Treat as grouped when propagating variant conditions                                                                  |

|                                                                                                                       |

| OK Cancel Help Apply                                                                                                  |

You are now ready to generate Structured Text code for your IDE. See "Generate and Examine Structured Text Code" on page 1-17.

#### Generate and Examine Structured Text Code

#### In this section...

"Generate Structured Text from the Model Window" on page 1-17

"Generate Structured Text with the MATLAB Interface" on page 1-19

"View Generated Code" on page 1-20

#### Generate Structured Text from the Model Window

You must already have set up your environment and Simulink model to use the Simulink PLC Coder software to generate Structured Text code. If you have not yet done so, see "Prepare Model for Structured Text Generation" on page 1-9.

- 1 If you do not have the plcdemo\_simple\_subsystem model open, open it now.

- 2 Right-click the Subsystem block and select PLC Code > Options.

The Configuration Parameters dialog box is displayed.

| 🚳 Configuration Parameters: plcden                                                                                                                                                                                                                                                    | no_simple_subsystem/Configuration                                                                                                   | (Active)                                                                        |      |        | _        |     | ×   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|------|--------|----------|-----|-----|

| ★ Commonly Used Parameters                                                                                                                                                                                                                                                            | ≡ All Parameters                                                                                                                    |                                                                                 |      |        |          |     | ^   |

| Select:<br>Solver<br>Data Import/Export<br>> Optimization<br>> Diagnostics<br>Hardware Implementation<br>Model Referencing<br>Simulation Target<br>> Code Generation<br>> Coverage<br>> HDL Code Generation<br>> Design Verifier<br>< PLC Code Generation<br>Comments<br>Optimization | General options<br>Target IDE<br>☑ Show full target list<br>Target IDE Path<br>Code Output Directory<br>☐ Generate testbench for su | 3S CoDeSys 2.3<br>F:\share\apps\3S-Software\CoDeSys\v2.3<br>./plcsrc<br>bsystem | 3    | Genera | ate code | ··· |     |

| Symbols<br>Report                                                                                                                                                                                                                                                                     |                                                                                                                                     |                                                                                 |      |        |          |     | ~   |

| 0                                                                                                                                                                                                                                                                                     |                                                                                                                                     |                                                                                 | ОК С | ancel  | Help     | Ap  | ply |

**3** On the **PLC Code Generation** pane, select an option from the **Target IDE** list, for example, **3S CoDeSys 2.3**.

The default **Target IDE** list displays the full set of supported IDEs. To see a reduced subset of the target IDEs supported by Simulink PLC Coder, disable the option **Show full target list**. To customize this list, use the plccoderpref function.

- 4 Click Apply.

- **5** Click Generate code.

This button:

- Generates Structured Text code (same as the PLC Code > Generate Code for Subsystem option)

- Stores generated code in model\_name.exp (for example, plcdemo\_simple\_subsystem.exp)

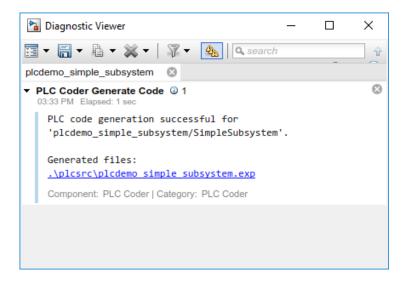

When code generation is complete, a **View diagnostics** hyperlink appears at the bottom of the model window. Click this hyperlink to open the Diagnostic Viewer window.

This window has links that you can click to open the associated files. For more information, see "Files Generated with Simulink PLC Coder" on page 1-23.

#### Generate Structured Text with the MATLAB Interface

You can generate Structured Text code for a subsystem in the Command Window with the plcgeneratecode function. You must have already configured the parameters for the model or, alternatively, you may use the default settings.

For example, to generate code from the SimpleSubsystem subsystem in the plcdemo\_simple\_subsystem model:

1 Open the plcdemo\_simple\_subsystem model:

plcdemo\_simple\_subsystem

**2** Open the Configuration Parameters dialog box using the plcopenconfigset function:

plcopenconfigset('plcdemo\_simple\_subsystem/SimpleSubsystem')

- **3** Select a target IDE.

- **4** Configure the subsystem as described in "Prepare Model for Structured Text Generation" on page 1-9.

- **5** Generate code for the subsystem:

generatedfiles = plcgeneratecode('plcdemo\_simple\_subsystem/SimpleSubsystem')

#### **View Generated Code**

After generating the code, you can view it in the MATLAB Editor. For a description of how the generated code for the Simulink components map to Structured Text components, see "PLC Code Generation Basics". In addition, note the following:

- Matrix data types: The coder converts matrix data types to single-dimensional vectors (column-major) in the generated Structured Text.

- Generated code header: If your model has author names, creation dates, and model descriptions, the generated code contains these items in the header comments. The header also lists fundamental sample times for the model and the subsystem block for which you generate code.

- Code comments: You can choose to propagate block descriptions to comments in generated code. See "Propagate Block Descriptions to Code Comments" on page 1-22.

The figure illustrates generated code for the CoDeSys Version 2.3 PLC IDE. Generated code for other platforms, such as Rockwell Automation RSLogix 5000, is in XML or other format and looks different.

```

15 FUNCTION BLOCK SimpleSubsystem

16

VAR_INPUT

17

ssMethodType: SINT;

18

U: LREAL;

1

19

END VAR

20

VAR OUTPUT

21

22

23

24

25

26

27

28

Y: LREAL;

END VAR

VAR

UnitDelay_DSTATE: LREAL;

END VAR

VAR TEMP

rtb_Gain: LREAL;

END VAR

29

CASE ssMethodType OF

30

SS INITIALIZE:

31

(* InitializeConditions for UnitDelay: '<S1>/Unit Delay' *)

32

UnitDelay DSTATE := 0;

33

34

SS OUTPUT:

(* Gain: '<S1>/Gain' incorporates:

35

* Inport: '<Root>/U'

36

37

* Sum: '<S1>/Sum'

38

39

40

41

42

43

44

45

46

47

* UnitDelay: '<S1>/Unit Delay'

*)

rtb Gain := (U - UnitDelay DSTATE) * 0.5;

(* Outport: '<Root>/Y' *)

Y := rtb_Gain;

(* Update for UnitDelay: '<S1>/Unit Delay' *)

UnitDelay DSTATE := rtb Gain;

48

END CASE:

49

END FUNCTION BLOCK

```

If you are confident that the generated Structured Text is good, optionally change your workflow to automatically generate and import code to the target IDE. For more information, see "Import Structured Text Code Automatically" on page 1-27.

### **Propagate Block Descriptions to Code Comments**

You can propagate block descriptions from the model to comments in your generated code.

For specific IDEs, you can propagate the block descriptions into specific XML tags in the generated code. The IDEs use the tags to create a readable description of the function blocks in the IDE.

- For Rockwell Automation RSLogix 5000 AOI/routine target IDEs, the coder propagates block descriptions from the model into the L5X AdditionalHelpText XML tag. The IDE can then import the tag as part of AOI and routine definition in the generated code.

- For CoDeSys 3.5 IDE, the coder propagates block descriptions from the model into the documentation XML tag. When you import the generated code into the CoDeSys 3.5 IDE, the IDE parses the content of this tag and provides readable descriptions of the function blocks in your code.

To propagate block descriptions to comments:

- **1** Enter a description for the block.

- **a** Right-click the block for which you want to write a description and select **Properties**.

- **b** On the **General** tab, enter a block description.

- **2** Before code generation, specify that block descriptions must propagate to code comments.

- **a** Right-click the subsystem for which you are generating code and select **PLC Code > Options**.

- **b** Select the option Include block description on page 13-16.

Your block description appears as comments in the generated code.

### Files Generated with Simulink PLC Coder

The Simulink PLC Coder software generates Structured Text code and stores it according to the target IDE platform. These platform-specific paths are default locations for the generated code. To customize generated file names, see "Specify Custom Names for Generated Files" on page 1-26.

| Platform                                         | Generated Files                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3S-Smart<br>Software<br>Solutions<br>CoDeSys 2.3 | <i>current_folder</i> \plcsrc\model_name.exp — Structured Text file for importing to the target IDE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3S-Smart<br>Software<br>Solutions<br>CoDeSys 3.3 | <i>current_folder</i> \plcsrc\model_name.xml — Structured Text file for importing to the target IDE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3S-Smart<br>Software<br>Solutions<br>CoDeSys 3.5 | <i>current_folder</i> \plcsrc\model_name.xml — Structured Text file for importing to the target IDE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| B&R<br>Automation<br>Studio IDE                  | <ul> <li>The following files in <i>current_folder</i>\plcsrc\model_name — Files for importing to the target IDE:</li> <li>Package.pkg — (If test bench is generated) Top-level package file for function blocks library and test bench main program in XML format.</li> <li>In the main folder (if test bench is generated):</li> <li>IEC.prg — Test bench main program definition file in XML format.</li> <li>mainInit.st — Text file. Test bench init program file in Structured Text.</li> <li>mainCyclic.st — Text file. Test bench exit program file in Structured Text.</li> <li>mainExit.st — Text file. Test bench exit program file in Structured Text.</li> <li>main.typ — Text file. Main program type definitions file in Structured Text.</li> </ul> |

| Platform                                              | Generated Files                                                                                                                                                                                                                                                                 |

|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Beckhoff<br>TwinCAT 2.11                              | <i>current_folder</i> \plcsrc\model_name.exp — Structured Text file for importing to the target IDE.                                                                                                                                                                            |

| Beckhoff<br>TwinCAT 3                                 | <i>current_folder</i> \plcsrc\model_name.xml — Structured Text file for importing to the target IDE.                                                                                                                                                                            |

| KW-Software<br>MULTIPROG<br>5.0                       | <i>current_folder</i> \plcsrc\model_name.xml — Structured Text file, in XML format, for importing to the target IDE.                                                                                                                                                            |

| Phoenix<br>Contact PC<br>WORX 6.0                     | <i>current_folder</i> \plcsrc\model_name.xml — Structured Text file, in XML format, for importing to the target IDE.                                                                                                                                                            |

| Rockwell<br>Automation<br>Studio 5000<br>IDE: AOI     | <i>current_folder</i> \plcsrc\model_name.L5X — (If test bench is generated)<br>Structured Text file for importing to the target IDE using Add-On Instruction<br>(AOI) constructs. This file is in XML format and contains the generated<br>Structured Text code for your model. |

| Rockwell<br>Automation<br>Studio 5000<br>IDE: Routine | <i>current_folder</i> \plcsrc\model_name.L5X — (If test bench is generated)<br>Structured Text file for importing to the target IDE using routine constructs. This<br>file is in XML format and contains the generated Structured Text code for your<br>model.                  |

|                                                       | In <i>current_folder</i> \plcsrc\model_name (if test bench is not generated), the following files are generated:                                                                                                                                                                |

|                                                       | • <i>subsystem_block_name</i> .L5X — Structured Text file in XML format.<br>Contains program tag and UDT type definitions and the routine code for the top-level subsystem block.                                                                                               |

|                                                       | • <i>routine_name</i> .L5X — Structured Text files in XML format. Contains routine code for other subsystem blocks.                                                                                                                                                             |

| Rockwell<br>Automation<br>RSLogix 5000<br>IDE: AOI    | <i>current_folder</i> \plcsrc\model_name.L5X — (If test bench is generated)<br>Structured Text file for importing to the target IDE using Add-On Instruction<br>(AOI) constructs. This file is in XML format and contains the generated<br>Structured Text code for your model. |

| Platform                                               | Generated Files                                                                                                                                                                                                                                                                                            |

|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rockwell<br>Automation<br>RSLogix 5000<br>IDE: Routine | <i>current_folder</i> \plcsrc\model_name.L5X — (If test bench is generated)<br>Structured Text file for importing to the target IDE using routine constructs. This<br>file is in XML format and contains the generated Structured Text code for your<br>model.                                             |

|                                                        | In <i>current_folder</i> \plcsrc\model_name (if test bench is not generated), the following files are generated:                                                                                                                                                                                           |

|                                                        | • <i>subsystem_block_name</i> .L5X — Structured Text file in XML format.<br>Contains program tag and UDT type definitions and the routine code for the top-level subsystem block.                                                                                                                          |

|                                                        | • <i>routine_name</i> .L5X — Structured Text files in XML format. Contains routine code for other subsystem blocks.                                                                                                                                                                                        |

| Siemens<br>SIMATIC<br>STEP 7 IDE                       | <pre>current_folder\plcsrc\model_name\model_name.scl — Structured Text file for importing to the target IDE. current_folder\plcsrc\model_name\model_name.asc — (If test bench</pre>                                                                                                                        |

|                                                        | is generated) Text file. Structured Text file and symbol table for generated test bench code.                                                                                                                                                                                                              |

| Siemens TIA<br>Portal IDE                              | <pre>current_folder\plcsrc\model_name\model_name.scl — Structured Text file for importing to the target IDE.</pre>                                                                                                                                                                                         |

| Generic                                                | <i>current_folder</i> \plcsrc\model_name.st — Pure Structured Text file. If<br>your target IDE is not available for the Simulink PLC Coder product, consider<br>generating and importing a generic Structured Text file.                                                                                   |

| PLCopen XML                                            | <i>current_folder</i> \plcsrc\model_name.xml — Structured Text file formatted<br>using the PLCopen XML standard. If your target IDE is not available for the<br>Simulink PLC Coder product, but uses a format like this standard, consider<br>generating and importing a PLCopen XML Structured Text file. |

| Rexroth<br>IndraWorks                                  | <i>current_folder</i> \plcsrc\model_name.xml — Structured Text file for importing to the target IDE.                                                                                                                                                                                                       |

| OMRON<br>Sysmac Studio                                 | <i>current_folder</i> \plcsrc\model_name.xml — Structured Text file for importing to the target IDE.                                                                                                                                                                                                       |

# **Specify Custom Names for Generated Files**

The Simulink PLC Coder software generates Structured Text code and stores it according to the target IDE platform. These platform-specific paths are default locations for the generated code. For more information, see "Files Generated with Simulink PLC Coder" on page 1-23.

To specify a different name for the generated files, set the **Function name options** parameter in the Subsystem block:

- 1 Right-click the Subsystem block for which you want to generate code and select Subsystem Parameters.

- 2 In the Main tab, select the Treat as atomic unit check box.

- **3** Click the **Code Generation** tab.

- **4** From the **Function Packaging** parameter list, select either **Nonreusable** function or **Reusable** Function.

These options enable the **Function name options** and **File name options** parameters.

**5** Select the option that you want to use for generating the file name.

| Function name options | Generated File Name                                                                                                                                    |  |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Auto                  | Default. Uses the model name, as listed<br>in "Prepare Model for Structured Text<br>Generation" on page 1-9, for example,<br>plcdemo_simple_subsystem. |  |

| Use subsystem name    | Uses the subsystem name, for example, SimpleSubsystem.                                                                                                 |  |

| User specified        | Uses the custom name that you specify<br>in the <b>Function name</b> parameter, for<br>example, SimpleSubsystem.                                       |  |

## Import Structured Text Code Automatically

### In this section...

"PLC IDEs That Qualify for Importing Code Automatically" on page 1-27

"Generate and Automatically Import Structured Text Code" on page 1-27

"Troubleshoot Automatic Import Issues" on page 1-28

## PLC IDEs That Qualify for Importing Code Automatically

If you are confident that your model produces Structured Text that does not require visual examination, you can generate and automatically import Structured Text code to one of the following target PLC IDEs:

- 3S-Smart Software Solutions CoDeSys Version 2.3

- KW-Software MULTIPROG Version 5.0

- Phoenix Contact PC WORX Version 6.0

- Rockwell Automation RSLogix 5000 Version 17, 18, or 19

For the Rockwell Automation RSLogix routine format, you must generate testbench code for automatic import and verification.

- Siemens SIMATIC STEP 7 Version 5.4 only for the following versions:

- Siemens SIMATIC Manager: Version V5.4+SP5+HF1, Revision K5.4.5.1

- S7-SCL: Version V5.3+SP5, Revision K5.3.5.0

- S7-PLCSIM: Version V5.4+SP3, Revision K5.4.3.0

Working with the default CoDeSys Version 2.3 IDE should require additional changes for only the KW-Software MULTIPROG 5.0 and Phoenix Contact PC WORX 6.0 IDE. For information about automatically importing Structured Text code to these IDEs, see "Import and Verify Structured Text to KW-Software MULTIPROG 5.0 and Phoenix Contact PC WORX 6.0 IDEs" on page 4-5.

## Generate and Automatically Import Structured Text Code

You can generate and automatically import Structured Text code. Before you start:

• In the target IDE, save your current project.

- Close open projects.

- Close the target IDE and target IDE-related windows.

**Note:** While the automatic import process is in progress, do not touch your mouse or keyboard. Doing so might disrupt the process. When the process completes, you can resume normal operations.

You must have already installed your target PLC IDE in a default location, and it must use the CoDeSys V2.3 IDE. If you installed the target PLC IDE in a nondefault location, open the Configuration Parameters dialog box. In the PLC Coder node, set the **Target IDE Path** parameter to the installation folder of your PLC IDE. See "Target IDE Path" on page 13-10.

- 1 If it is not already started, open the Command Window.

- 2 Open the plcdemo\_simple\_subsystem model.

- 3 Right-click the Subsystem block and select PLC Code > Generate and Import Code for Subsystem.

The software:

- **a** Generates the code.

- **b** Starts the target IDE interface.

- c Creates a new project.

- **d** Imports the generated code to the target IDE.

If you want to generate, import, and run the Structured Text code, see "Import and Verify Structured Text Code" on page 4-4.

### **Troubleshoot Automatic Import Issues**

Following are guidelines, hints, and tips for questions or issues you might have while using the automatic import capability of the Simulink PLC Coder product.

### Supported Target IDEs

The Simulink PLC Coder software supports only the following versions of target IDEs for automatic import and verification:

- 3S-Smart Software Solutions CoDeSys Version 2.3

- KW-Software MULTIPROG 5.0 (English)

- Phoenix Contact PC WORX 6.0 (English)

- Rockwell Automation RSLogix 5000 Series Version 17, 18, 19 (English)

For the Rockwell Automation RSLogix routine format, you must generate testbench code for automatic import and verification.

• Siemens SIMATIC STEP 7 Version 5.4 (English and German)

### **Unsupported Target IDEs**

The following target IDEs currently do not support automatic import. For these target IDEs, the automatic import menu items (Generate and Import Code for Subsystem and Generate, Import, and Verify Code for Subsystem) are disabled.

- 3S-Smart Software Solutions CoDeSys Version 3.3

- 3S-Smart Software Solutions CoDeSys Version 3.5

- B&R Automation Studio IDE

- Beckhoff TwinCAT 2.11, 3

- Generic

- PLCopen

- Rockwell Automation Studio 5000 Logix Designer (both routine and AOI constructs)

### **Possible Automatic Import Issues**

When the Simulink PLC Coder software fails to finish automatically importing for the target IDE, it reports an issue in a message dialog box. To remedy the issue, try the following actions:

- Check that the coder supports the target IDE version and language setting combination.

- Check that you have specified the target IDE path in the subsystem Configuration Parameters dialog box.

- Close currently open projects in the target IDE, close the target IDE completely, and try again.

- Some target IDEs can have issues supporting the large data sets the coder test bench generates. In these cases, try to shorten the simulation cycles to reduce the data set size, then try the automatic import again.

• Other applications can interfere with automatic importing to a target IDE. Try to close other unrelated applications on the system and try the automatic import again.

# Simulation and Code Generation of Motion Instructions

| In this section                                                |  |

|----------------------------------------------------------------|--|

| "Workflow for Using Motion Instructions in Model" on page 1-31 |  |

| "Library of Motion Instructions" on page 1-34                  |  |

| "Data Types for Motion Instructions" on page 1-34              |  |

| "Limitations for MAM Instruction" on page 1-35                 |  |

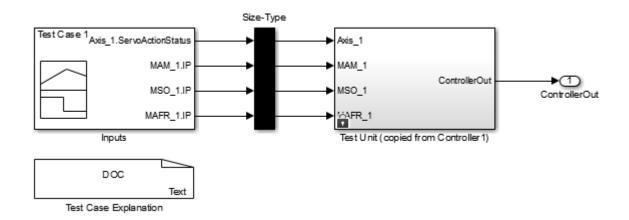

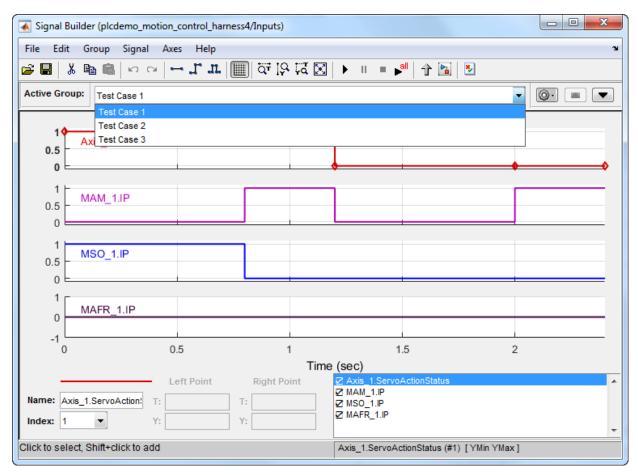

The Simulink PLC Coder software supports a workflow for the behavioral simulation and code generation of motion instructions for the Rockwell Automation RSLogix 5000 IDE.

## Workflow for Using Motion Instructions in Model

This workflow uses plcdemo\_motion\_control in the plcdemos folder. This example provides a template that you can use with motion instructions. It contains the following subsystems.

| Subsystem       | Description                                                                                                                                                                                                                           |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Controller      | Contains an example Stateflow chart with motion<br>instructions. The controller subsystem sends input<br>to the Command Profile subsystem (part of the<br>template).<br>Replace this subsystem with your own controller<br>subsystem. |

| Command Profile | Contains a utility subsystem in which the coder<br>calculates the position data based on the parameters<br>of the motion instructions MAM command.                                                                                    |

| Drive Model     | Contains a minimalistic drive model.<br>Replace this subsystem with your own drive model<br>subsystem.                                                                                                                                |

| Drive Status    | Contains a utility subsystem that reads drive status<br>and returns that status to the Controller subsystem.<br>Typically, you do not need to modify or replace this<br>subsystem.                                                    |

Before you start, create:

- A custom controller subsystem. This subsystem contains motion instructions. The controller subsystem sends input to the Command Profile subsystem.

- A custom drive (plant) model subsystem. The subsystem sends input to a Drive Status subsystem. Design the subsystem to work with the inputs and outputs.

To modify the plcdemo\_motion\_control example:

- 1 Open the plcdemo\_motion\_control example template.

- **2** In the Controller subsystem, replace the ExampleController chart with your controller subsystem.

- 3 In the template, replace the Drive Model subsystem with your drive (plant) model.

- **4** Simulate the model.

- **5** Observe the simulation results in the model scopes.

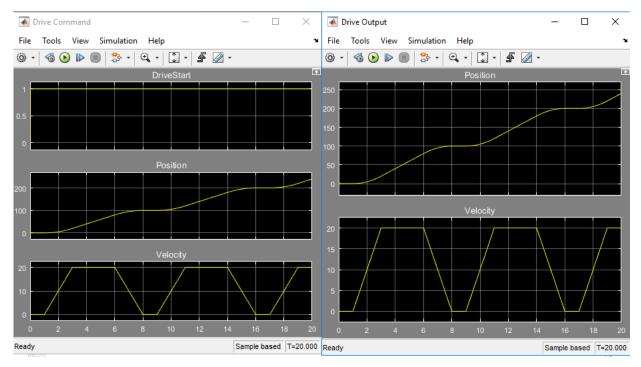

The following plots show the output from plcdemo\_motion\_control without modification.

6 Generate code for the example model. To view the code in HTML format on page 5-4, in the coder configuration parameters, select the PLC Code Generation > Report > Generate traceability report check box and click Apply.

Navigate to the PLC Code Generation node and click Generate code.

An HTML file of the generated code is displayed.

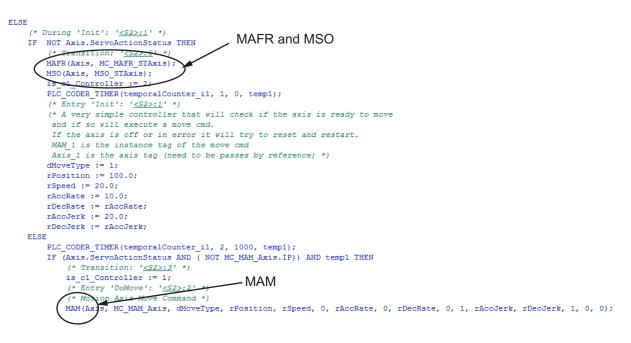

7 Observe the generated code for MAM, MAFR, and MSO.

## Library of Motion Instructions

The plcdemo\_motion\_control example uses a motion instructions library that contains a Motion Stub Functions Stateflow chart. This chart defines stub functions for only the following motion instructions:

- MAM

- MAFR

- MSO

To use other Rockwell Automation RSLogix motion instructions in the model, you must define your own stub functions to correspond to the RSLogix motion instructions in the Motion Stub Functions chart.

### Data Types for Motion Instructions

The plcdemo\_motion\_control example uses Simulink bus data types (Simulink.Bus). These data types correspond to the motion instruction AXIS and

MOTION\_INSTRUCTION user-defined data types (UDTs) in the Rockwell Automation RSLogix 5000 IDE. For these UDTs, the example defines only the fields used in the ExampleController chart of the plcdemo\_motion\_control example. When you generate code, the coder maps the bus data types to the motion instruction UDTs. If your controller subsystem uses other fields of motion instruction UDTs, you must add them to the definition of the corresponding Simulink bus data types. The /toolbox/plccoder/ plccoderdemos/PLCMotionType.mat file contains the definitions of the Simulink bus data types. You can add more fields to these definitions as required by your controller.

| Name               | Size | Bytes Class  | Attributes |

|--------------------|------|--------------|------------|

| AXIS_SERVO_DRIVE   | 1x1  | Simulink.Bus |            |

| MOTION_INSTRUCTION | 1x1  | Simulink.Bus |            |

### Limitations for MAM Instruction

In the plcdemo\_motion\_control example, the MAM instruction has the following limitations:

- Direction parameter is always forward.

- The software supports only the Trapezoidal profile.

- The software ignores units parameters.

- The software does not support Merge and Merge speed.

# Mapping Simulink Semantics to Structured Text

- "Generated Code Structure for Simple Simulink Subsystems" on page 2-2

- "Generated Code Structure for Reusable Subsystems" on page 2-4

- "Generated Code Structure for Triggered Subsystems" on page 2-7

- "Generated Code Structure for Stateflow Charts" on page 2-9

- "Generated Code Structure for MATLAB Function Block" on page 2-14

- "Generated Code Structure for Multirate Models" on page 2-16

- "Generated Code Structure for Subsystem Mask Parameters" on page 2-18

- "Global Tunable Parameter Initialization for PC WORX" on page 2-23

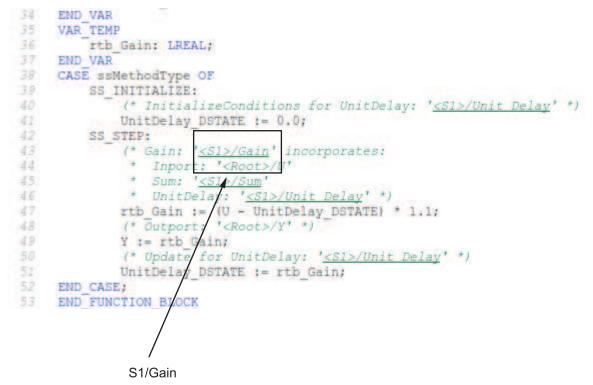

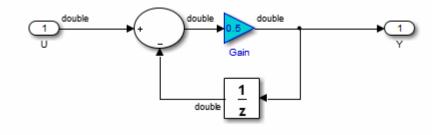

# Generated Code Structure for Simple Simulink Subsystems

This topic assumes that you have generated Structured Text code from a Simulink model. If you have not yet done so, see "Generate Structured Text from the Model Window" on page 1-17.

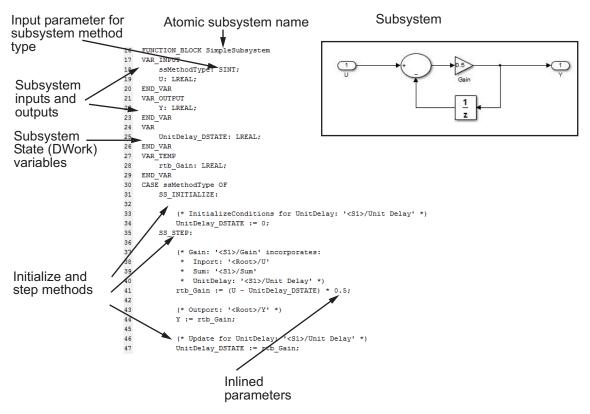

The example in this topic shows generated code for the CoDeSys Version 2.3 IDE. Generated code for other IDE platforms looks different.

1 If you do not have the plcdemo\_simple\_subsystem.exp file open, open it in the MATLAB editor. In the folder that contains the file, type:

edit plcdemo\_simple\_subsystem.exp

A file like the following is displayed.

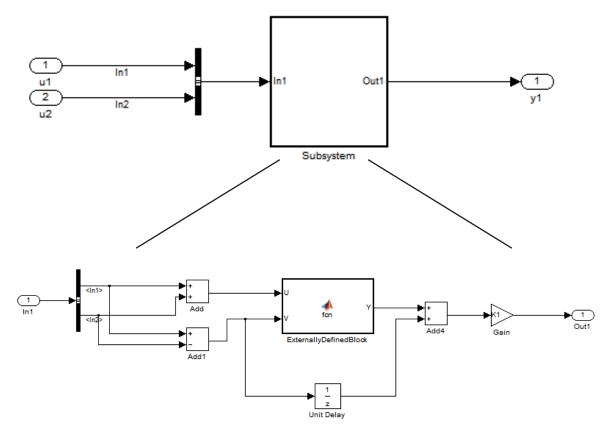

The following figure illustrates the mapping of the generated code to Structured Text components for a simple Simulink subsystem. The Simulink subsystem corresponds to the Structured Text function block, Subsystem.

Note: The coder maps alias data types to the base data type in the generated code.

2 Inspect this code as you ordinarily do for PLC code. Check the generated code.

**Note:** The Simulink model for plcdemo\_simple\_subsystem does not contain signal names at the input or output of the SimpleSubsystem block. So the generated code has the port names U and Y as the input and output variable names of the FUNCTION\_BLOCK. However, even if your model does contain signal names, coder only uses port names in the generated code.

# Generated Code Structure for Reusable Subsystems

This topic assumes that you have generated Structured Text code from a Simulink model. If you have not yet done so, see "Generate Structured Text from the Model Window" on page 1-17.

The example in this topic shows generated code for the CoDeSys Version 2.3 IDE. Generated code for other IDE platforms looks different.

- 1 Open the plcdemo\_reusable\_subsystem model.

- 2 Right-click the Subsystem block and select PLC Code > Generate Code for Subsystem.

The Simulink PLC Coder software generates Structured Text code and places it in *current\_folder/plcsrc/plcdemo\_reusable\_subsystem.exp*.

3 If you do not have the plcdemo\_reusable\_subsystem.exp file open, open it in the MATLAB editor.

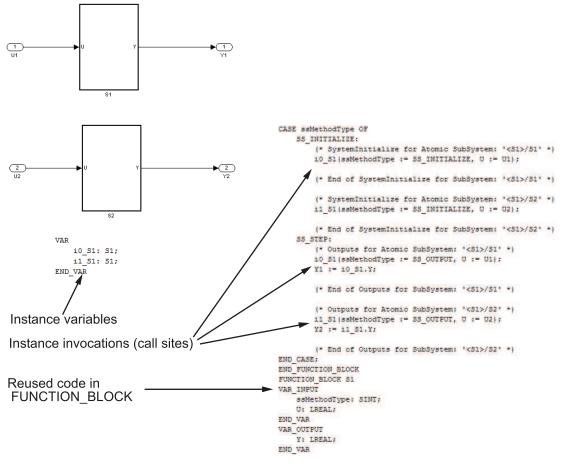

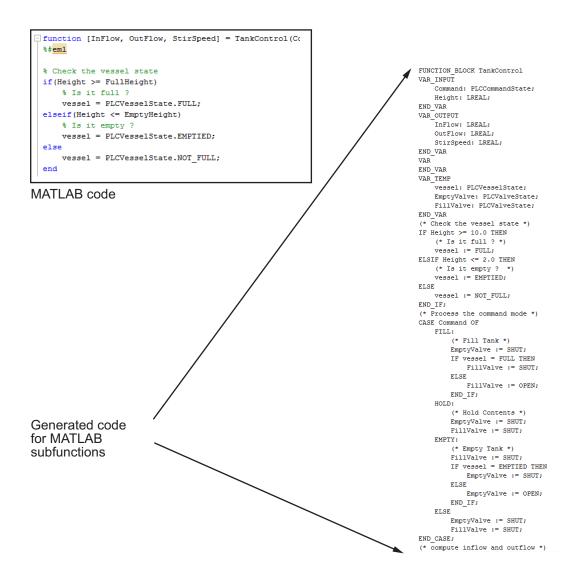

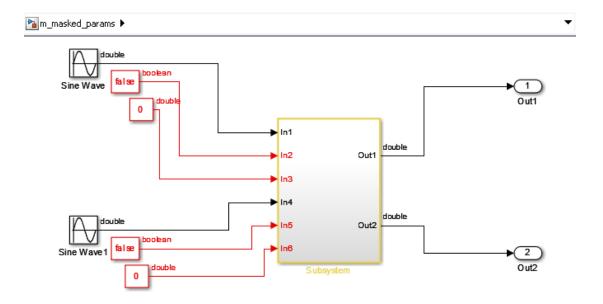

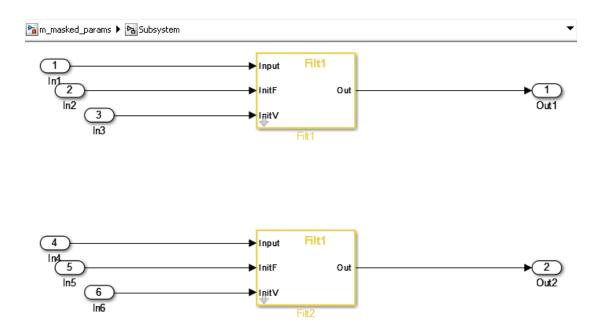

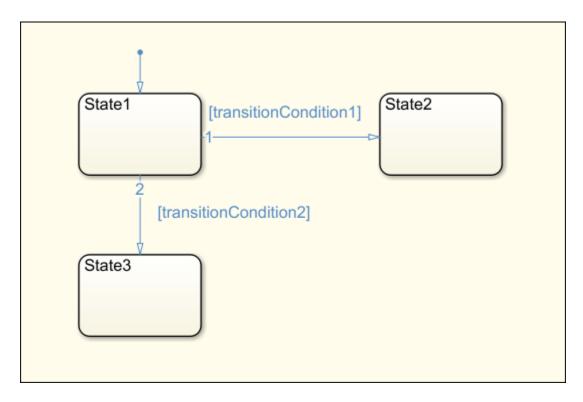

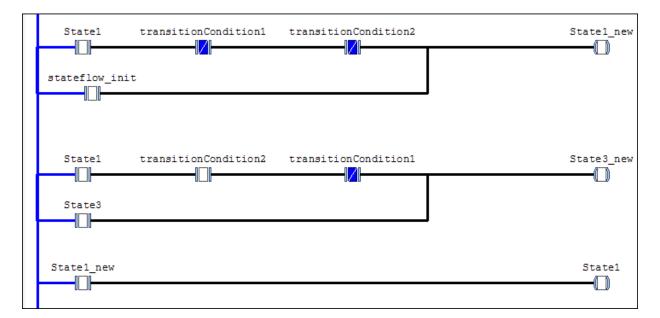

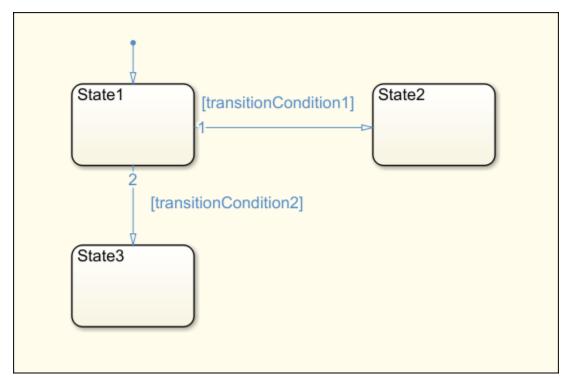

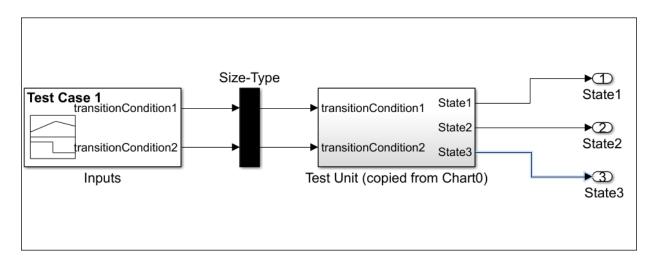

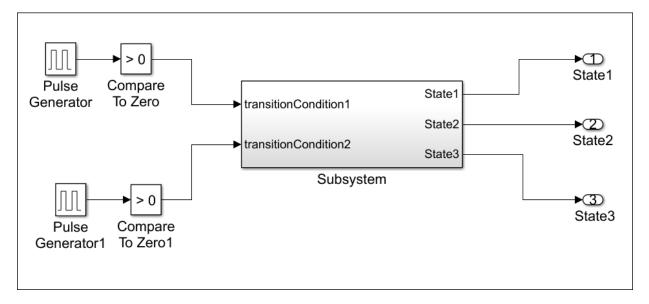

The following figure illustrates the mapping of the generated code to Structured Text components for a reusable Simulink subsystem. This graphic contains a copy of the hierarchical subsystem, ReusableSubsystem. This subsystem contains two identical subsystems, S1 and S2. This configuration enables code reuse between the two instances (look for the ReusableSubsystem string in the code).